Grunwald Letnikov

Grunwald Letnikov

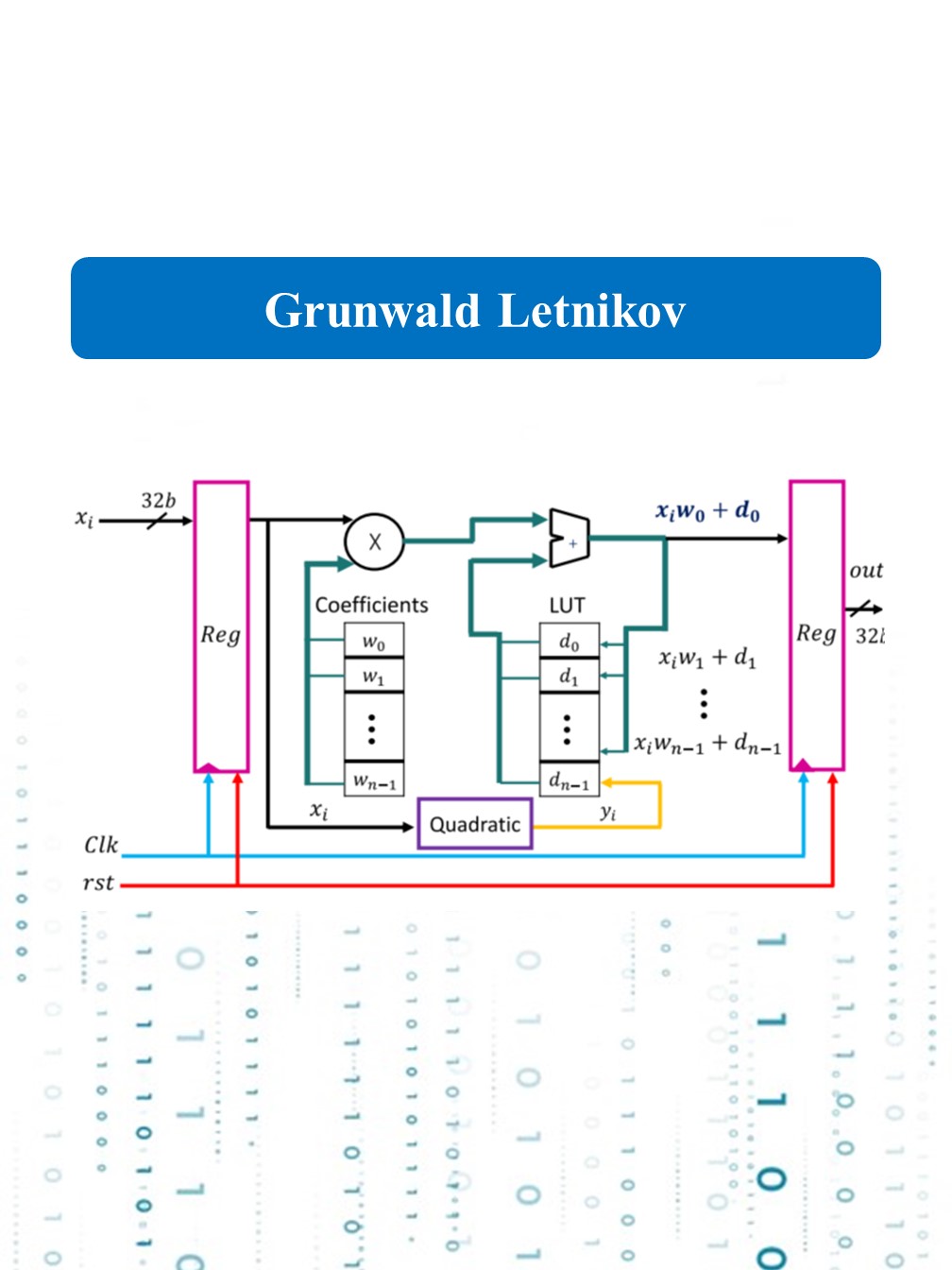

The design and hardware implementation of the GL integrator/differentiator are illustrated in Figure. The input and output signals are 32-bit fixed-point numbers, with 8 bits for the integer part and 24 bits for the fractional part. The proposed design is divided into two main parts. The first part is the fixed window, which includes the multiplication of coefficients W0 through W(n-1) with the input signal, as presented in Fig. 7. The second part is the quadratic approximation, which computes the output based on a quadratic equation. The first part of the design uses two LUTs: one stores the binomial coefficients W0 through W(n-1), and the other stores the output of the adder from xi * W0 + d0 through xi * W(n-1) + d(n-1). As shown in Figure, the hardware architecture of the GL operator operates as follows: each input value xi is multiplied by all the coefficients stored in the LUT. The results of these multiplications are added to the data previously stored in the LUT (d0 through d(n-1)). The operations from xi * W1 + d1 through xi * W(n-1) + d(n-1) are stored in the LUT at d0 through d(n-2). The last position, d(n-1), in the LUT is used to store the output of the second part of the design. The result, xi * W0 + d0, is taken as the output at each clock cycle.