Breadcrumb

Semi-Fragile Watermark for the Authentication and Recovery of Tampered Images

In order to strengthen the safety of corporate multimedia assets, a semi-fragile watermarking method is developed, which makes use of the integer wavelet transform (IWT) and the discrete cosine transform (DCT) for tamper detection and recovery. In this paper, we produce two distinct kinds of watermarks: an authentication watermark and a recovery watermark. A tamper detection methodology is utilized at the receiving end to check the watermarked image for validity and detect any assaults. If the changes are determined to be malicious, the suggested tamper recovery method is used to restore the

Modified Arnold Transform and DNA Manipulation for Chaos-Based RGB Image Encryption

Multimedia applications use image encryption algorithms extensively to safeguard and authenticate digital images. This paper presents an RGB image encryption method, which uses Chaos, DNA, pixel sum, and modified Arnold transform. The suggested algorithm is validated to be robust and resistant to visual, statistical, differential, and brute-force attacks. Additionally, the resulting encrypted images pass all tests of the NIST SP 800-22 test suite. © 2023 IEEE.

Energy Aware Tikhonov-Regularized FPA Technique for Task Scheduling in Wearable Biomedical Devices

Harvesting the energy from environmental sources is a promising solution for perpetual and continuous operation of biomedical wearable devices. Although the energy harvesting technology ensures the availability of energy source, yet power management is crucial to ensure prolonged and stable operation under a stringent power budget. Thus, power-aware task scheduling can play a key role in minimizing energy consumption to improve system durability while maintaining device functionality. This chapter proposes a novel biosensor task scheduling of energy harvesting-based biomedical wearable devices

Realistic Wireless Smart-Meter Network Optimization Using Composite RPL Metric

In smart metering applications, transferring and collecting data within delay constraints is crucial. IoT devices are usually resource-constrained and need reliable and energy-efficient routing protocol. Furthermore, meters deployed in lossy networks often lead to packet loss and congestion. In smart grid communication, low latency and low energy consumption are usually the main system targets. Considering these constraints, we propose an enhancement in RPL to ensure link reliability as well as low latency. We refer to the proposed new additive composite metric as Delay-Aware RPL (DA-RPL)

Medical Image Compression Based on Region of Interest

Medical images show a great interest since it is needed in various medical applications. In order to decrease the size of medical images which are needed to be transmitted in a faster way; Region of Interest (ROI) and hybrid lossless compression techniques are applied on medical images to be compressed without losing important data. In this paper, a proposed model will be presented and assessed based on size of the image, the Peak Signal to Noise Ratio (PSNR), and the time that is required to compress and reconstruct the original image. The major objective of the proposed model is to minimize

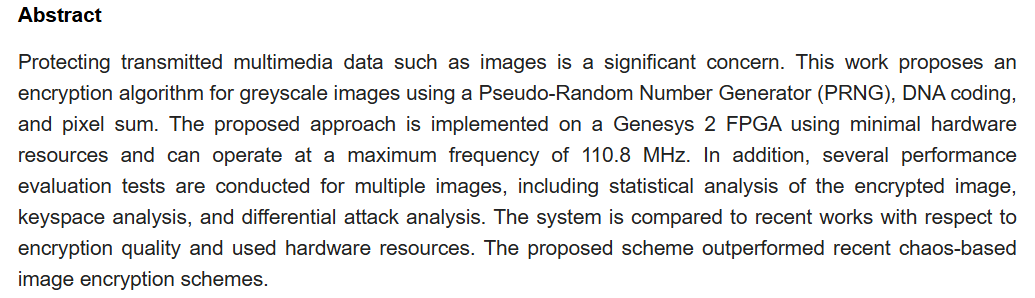

A Lightweight Image Encryption Scheme Using DNA Coding and Chaos

Protecting transmitted multimedia data such as images is a significant concern. This work proposes an encryption algorithm for greyscale images using a Pseudo-Random Number Generator (PRNG), DNA coding, and pixel sum. The proposed approach is implemented on a Genesys 2 FPGA using minimal hardware resources and can operate at a maximum frequency of 110.8 MHz. In addition, several performance evaluation tests are conducted for multiple images, including statistical analysis of the encrypted image, keyspace analysis, and differential attack analysis. The system is compared to recent works with

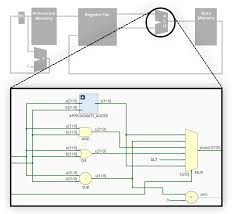

Single-Cycle MIPS Processor based on Configurable Approximate Adder

Enhancing computer architecture performance is a significant concern for architecture designers and users. This paper presents a novel approach to computer architecture design by using an approximate adder with configurable accuracy in a single-cycle MIPS processor as a study case. Using approximate adders decreased the delay on the expense of the design area. Using approximate computing with the MIPS processor, the timing performance has been improved by 253.4% compared to the lookahead adder. It has been implemented and tested using System-Verilog. © 2022 IEEE.

Adsorption as an Emerging Technology and Its New Advances of Eco-Friendly Characteristics: Isotherm, Kinetic, and Thermodynamic Analysis

Water contamination with paints causes a colour agent to the water that negatively affects the environment, organisms, and humans. Different physicochemical processes are applied for wastewater treatment; however, they have many drawbacks such as high cost, generating toxic waste, and non-effective at low concentrations. Adsorption is considered a promising technique for pollutant removal from polluted wastewater. Commercial activated carbon, nano-materials, and natural biological materials are used as adsorbents in adsorption. This chapter focuses on discussing the adsorption process, the

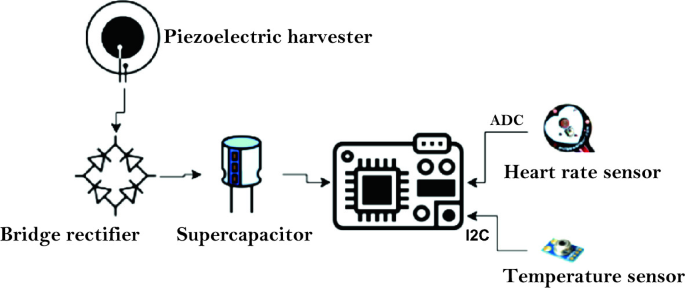

Sustainable Energy-Aware Task Scheduling for Wearable Medical Device Using Flower Pollination Algorithm

Power management and energy conservation are crucial for medical wearable devices that rely on energy harvesting. These devices operate under strict power budgets and require prolonged and stable operation. To achieve this, Energy-aware task scheduling is proposed as a solution to minimize energy consumption while ensuring the continued operational capabilities of the device. our paper presents a task scheduling method using the Flower Pollination Algorithm (FPA). The proposed task scheduling focuses on managing the activity of key components such as the heart rate sensor, temperature sensor

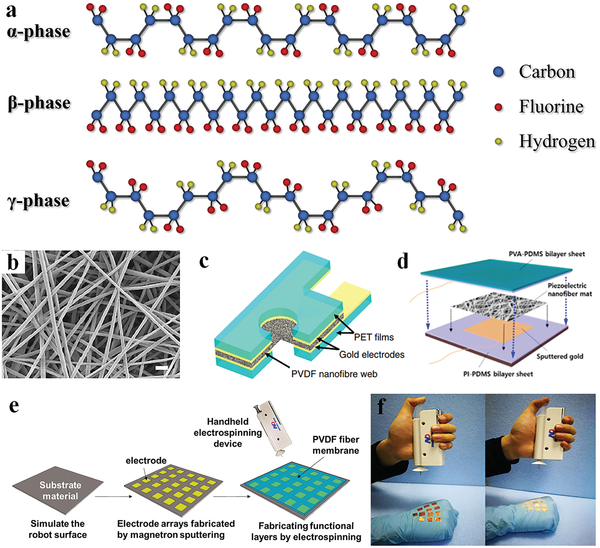

Improvement of piezoresistive pressure sensor using zig-zag shaped and PVDF material

Due to a wide range of applications in the biomedical industry, the need for flexible and wearable sensors is growing every day. A pressure sensor generates a signal based on the applied pressure. Sensors have become an integral component of our daily lives, from personal gadgets to industrial machinery. The identification of the low signal from the body necessitates the use of particularly sensitive sensors. The development of a pressure sensor that can transform the maximum input signal into an electrical output is critical. In this paper, zig-zag piezoresistors on a square diaphragm were

Pagination

- Previous page ‹‹

- Page 2

- Next page ››