Breadcrumb

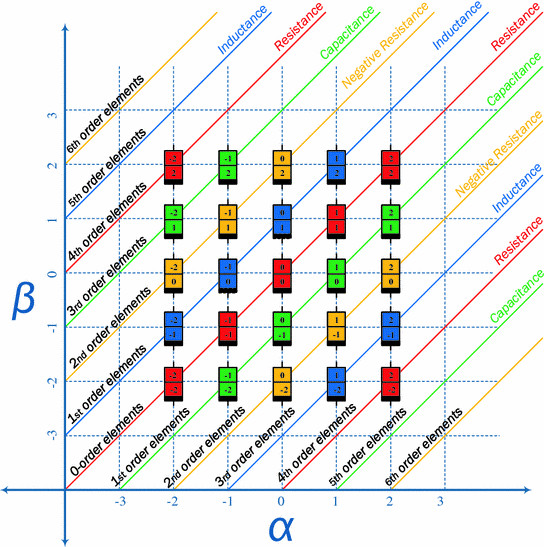

Fractional-Order Two-Port Networks

We introduce the concept of fractional-order two-port networks with particular focus on impedance and admittance parameters. We show how to transform a 2 × 2 impedance matrix with fractional-order impedance elements into an equivalent matrix with all elements represented by integer-order impedances; yet the matrix rose to a fractional-order power. Some examples are given. © 2016 M. E. Fouda et al.

Compact Wide Frequency Range Fractional-Order Models of Human Body Impedance against Contact Currents

Three circuit models using constant phase elements are investigated to represent the human body impedance against contact currents from 40 Hz to 110 MHz. The parameters required to represent the impedance are determined using a nonlinear least squares fitting (NLSF) applied to the averaged human body impedance dataset. The three fractional-order models with 4, 6, and 7 parameters are compared to an already existing integer-order, 11-parameter model. Simulations of the fractional-order models impedance are presented and discussed along with their limitations. © 2016 Todd J. Freeborn et al.

Memcapacitor based applications

This chapter is divided into three sections focusing on some memcapacitor-based applications. The first one discusses the mathematical analyses and design of resistive-less memcapacitor-based relaxation oscillators where different cases have been investigated and validated. Analytical expressions for the oscillation frequency, duty cycle, stored energy, and conditions of oscillation have been achieved with many numerical examples and circuit simulations. The second section discusses the boundary effect on the analysis and output behavior of memcapacitor-based oscillators compared to the

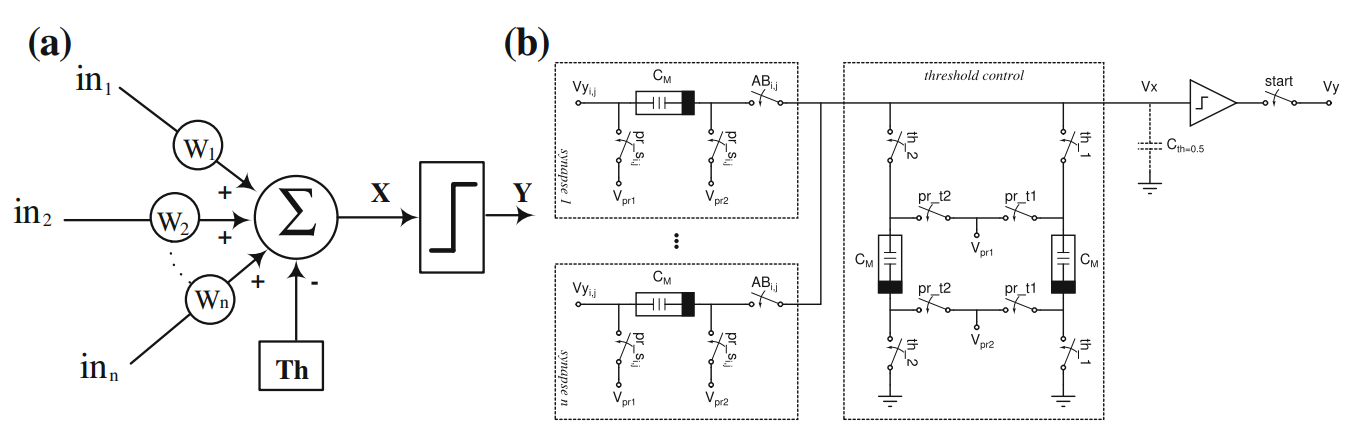

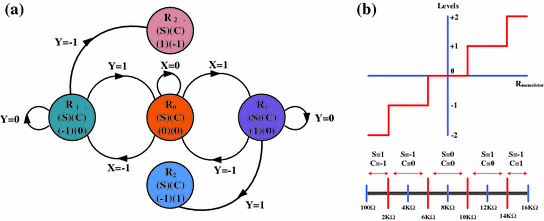

Memristor-based multilevel digital systems

This chapter investigates the advantages of memristor-based digital applications using multi-level arithmetic concepts. Recently, there are huge concerns regarding the memristor in digital signal processing (DSP) circuits to enhance the performance and realize very high density, nonvolatile memories in neural networks. This can be achieved by mapping the high/low logic into the memristor high/low resistances. Recently, the potential to divide the memristance levels to build multilevel digital circuits such as the ternary and redundant circuits are discussed. The concepts have been initiated by

Memcapacitor: Modeling, analysis, and emulators

This chapter reviews the memcapacitor, mathematical representations of time-invariant, physical realizations, and mathematical models. Moreover, the nonlinear boundary effect of the memcapacitor under step, sinusoidal, and general periodic excitation responses are discussed with analytical, numerical, and circuit simulations for different examples. The general analyses of series and parallel connections of memcapacitors are introduced with many examples and circuit simulations. Finally a charge-controlled, memristor-less memcapacitor is introduced and validated through different cases. © 2015

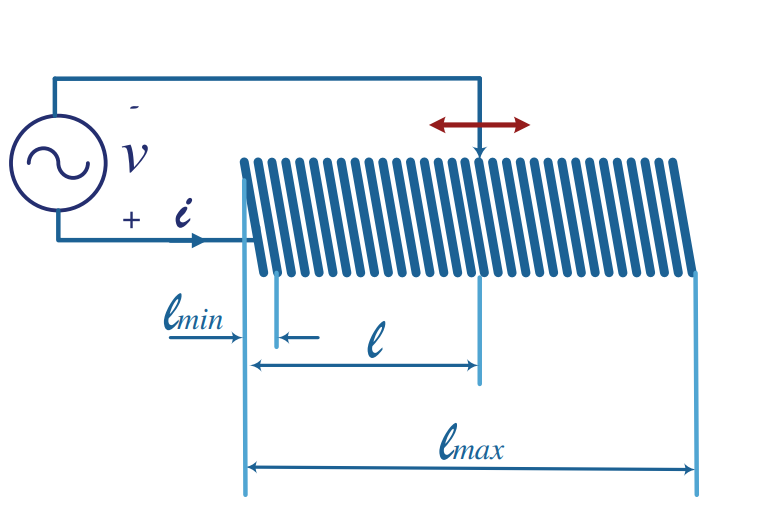

Meminductor: Modeling, analysis, and emulators

This chapter introduces the basic definition of meminductor and its mathematical representation of time-invariant system (Ideal, Generic, and Extended) with some examples. The mathematical model of meminductor and its response under different current excitations (step, sinusoidal, and periodic) are discussed with analytical, numerical, and circuit simulations. Different meminductor emulators are introduced with their mathematical modeling and numerical simulation, and verified using PSPICE simulations. © 2015, Springer International Publishing Switzerland.

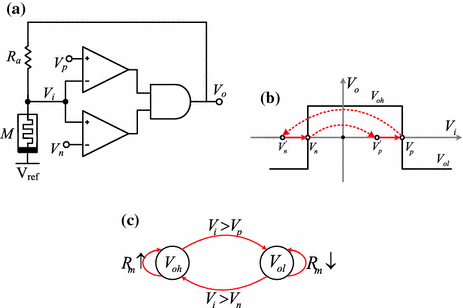

Memristor-based relaxation oscillator circuits

This chapter discusses the analysis and design of memristor-based oscillators which is considered one of the nonlinear analog block required for many applications such as chaotic memristor oscillators and artificial neuron network. The realizations of memristor-based oscillators have been discussed via replacing capacitors with memristors to construct relaxation reactance-less oscillators. The advantages of such oscillators are related to low frequency, nanoscale, and simple designs and can be used in neuromorphic systems. Different topologies of memristor-based relaxation oscillators have

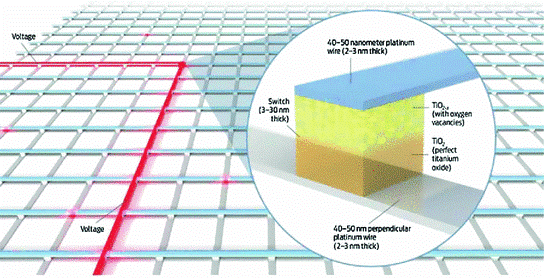

Memristor: Models, types, and applications

This chapter discusses the main properties of the memristor, a comparison between five recent memristor models, mathematical modeling of the HP memristor with analytical expressions for different excitations, mathematical representations of time-invariant memristor (ideal, generic, and extended), different memristor implementation types, and some memristor-based applications in digital and analog circuits. © 2015, Springer International Publishing Switzerland.

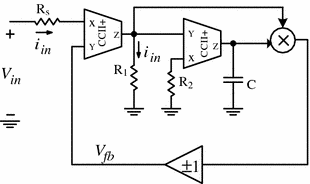

Memristor mathematical models and emulators

This chapter introduces different generalized mathematical classes of memristors which can be categorized as: continuous symmetrical models (current and voltage controlled emulators), continuous nonsymmetrical model, switched-memristor model, and fractional-order model with some experimental results. Different emulators with experimental results are discussed based on CCII, discrete components, and MOS realizations. Different analytical expressions, numerical analyses, circuit simulations results as well as experimental results are provided for most of the previous models. © 2015, Springer

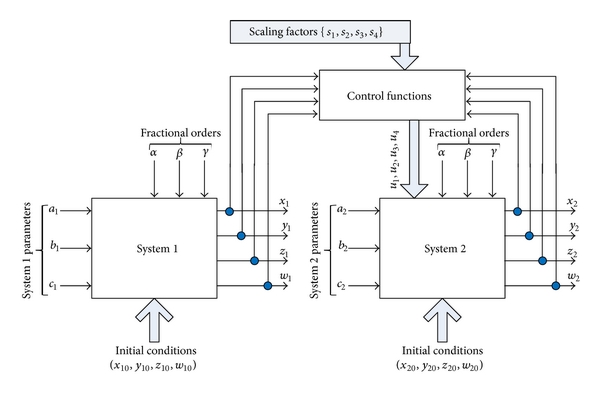

Amplitude modulation and synchronization of fractional-order memristor-based Chua's circuit

This paper presents a general synchronization technique and an amplitude modulation of chaotic generators. Conventional synchronization and antisynchronization are considered a very narrow subset from the proposed technique where the scale between the output response and the input response can be controlled via control functions and this scale may be either constant (positive, negative) or time dependent. The concept of the proposed technique is based on the nonlinear control theory and Lyapunov stability theory. The nonlinear controller is designed to ensure the stability and convergence of

Pagination

- Previous page ‹‹

- Page 36

- Next page ››