Breadcrumb

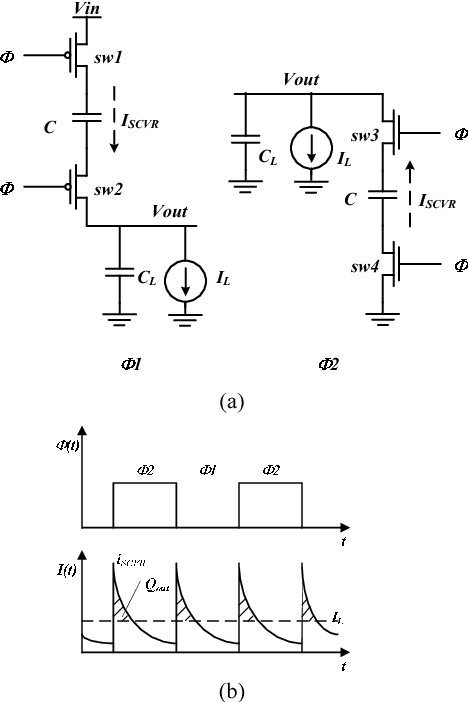

A novel control technique to eliminate output-voltage-ripple in switched-capacitor DC-DC converters

A novel ripple mitigation technique is proposed for switched-capacitor voltage regulators (SCVR), which eliminates the output voltage ripple without using multi-phase interleaving. An inner control loop matches the SCVR's switch current to the load current on a cycle by cycle basis. A 2-phase 32 SCVR is designed in 45-nm CMOS process with the proposed control. For a 1.8 V to 1.05 V /40 mA converter, the proposed mitigation loop reduces the peak-to-peak output ripple from 330 mVp-p to 17 mVp-p, using total output capacitance of 4 nF/A. In addition, the proposed technique yields excellent

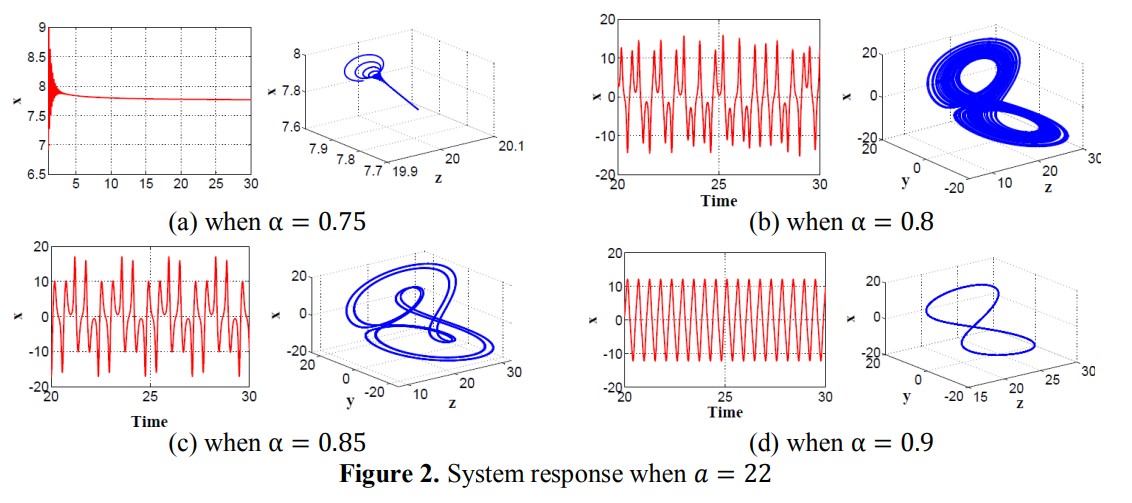

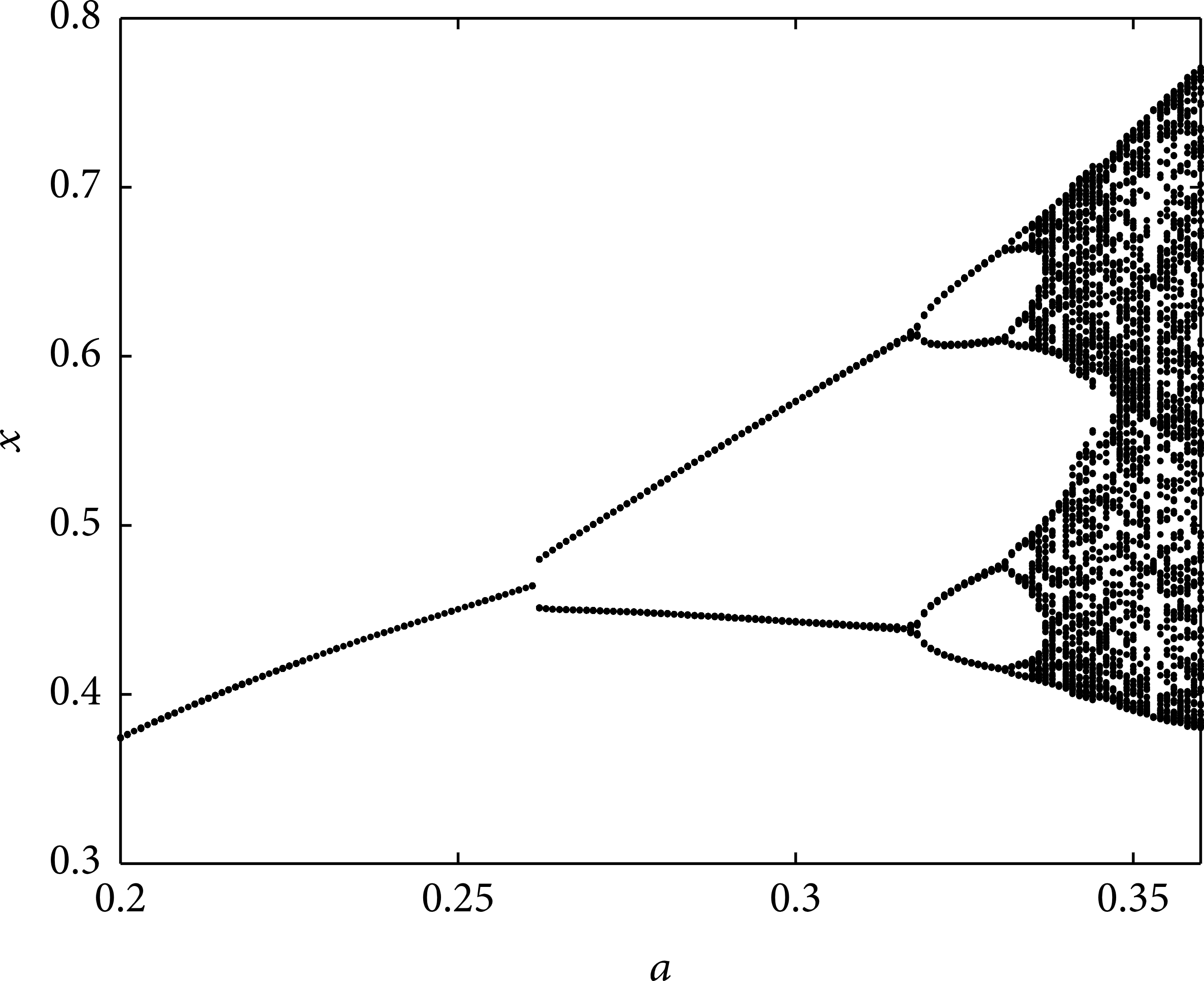

Parametric control on fractional-order response for Lü chaotic system

This paper discusses the influence of the fractional order parameter on conventional chaotic systems. These fractional-order parameters increase the system degree of freedom allowing it to enter new domains and thus it can be used as a control for such dynamical systems. This paper investigates the behaviour of the equally-fractional-order Lü chaotic system when changing the fractional-order parameter and determines the fractional-order ranges for chaotic behaviour. Five different parameter values and six fractional-order cases are discussed through this paper. Unlike the conventional

A novel chaotic system without equilibrium: Dynamics, synchronization, and circuit realization

A few special chaotic systems without unstable equilibrium points have been investigated recently. It is worth noting that these special systems are different from normal chaotic ones because the classical Shilnikov criterion cannot be used to prove chaos of such systems. A novel unusual chaotic system without equilibrium is proposed in this work. We discover dynamical properties as well as the synchronization of the new system. Furthermore, a physical realization of the system without equilibrium is also implemented to illustrate its feasibility. © 2017 Ahmad Taher Azar et al.

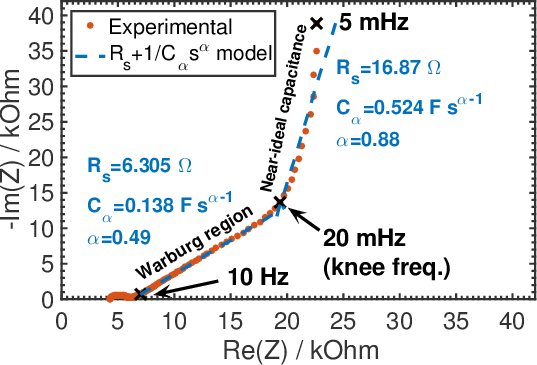

Variability of supercapacitor fractional-order parameters extracted from discharging behavior using least squares optimization

In this paper the variability of supercapacitor fractional-order model parameters are explored when extracted using a non-linear least squares optimization applied to their constant current discharging behaviour. The variability of parameters extracted 1000 different times applying the optimization process to multiple sets of simulated and experimental data are presented to validate this approach. The experimental results were collected from 4 samples of Panasonic EEC-SSR5H105 supercapacitors (1 F rating) acting as a secondary power source for an Arduino Uno system. Simulations using the

Fractional-order mihalas-niebur neuron model implementation using current-mirrors

A simple realization of the fractional-order Mihalas-Niebur neuron model is presented in this work. The required low-pass filter is implemented using current-mirrors offering simple circuitry and, also, electronic tunability of the realized time-constant. Due to the limited bandwidth required for this application, the necessary fractional-order capacitor is realized using an appropriately configured second-order RC network. The proposed realization highlights the connection between the fractional-order and the frequency spiking of the model through appropriate simulation results, which are

Possibility of information encoding/decoding using the memory effect in fractional-order capacitive devices

In this study, we show that the discharge voltage pattern of a supercapacitor exhibiting fractional-order behavior from the same initial steady-state voltage into a constant resistor is dependent on the past charging voltage profile. The charging voltage was designed to follow a power-law function, i.e. [Formula: see text], in which [Formula: see text] (charging time duration between zero voltage to the terminal voltage [Formula: see text]) and p ([Formula: see text]) act as two variable parameters. We used this history-dependence of the dynamic behavior of the device to uniquely retrieve

Advance Interconnect Circuit Modeling Design Using Fractional-Order Elements

Nowadays, the interconnect circuits' conduct plays a crucial role in determining the performance of the CMOS systems, especially those related to nano-scale technology. Modeling the effect of such an influential component has been widely studied from many perspectives. In this article, we propose a new general formula for RLC interconnect circuit model in CMOS technology using the fractional-order elements approach. The study is based on approximating an infinite transfer function of the CMOS circuit with a noninteger distributed RLC load to a finite number of poles. It is accurate due to the

FPGA implementation of a reconfigurable Viterbi decoder for WiMAX receiver

Field Programmable Gate Array technology (FPGA) is a highly configurable option for implementing many sophisticated signal processing tasks in Software Defined Radios (SDRs). Those types of radios are realized using highly configurable hardware platforms. Convolutional codes are used in every robust digital communication system and Viterbi algorithm is employed in wireless communications to decode the convolutional codes. Such decoders are complex and dissipate large amount of power. In this paper, a low power-reconfigurable Viterbi decoder for WiMAX receiver is described using a VHDL code for

FPGA implementation of a configurable viterbi decoder for software radio receiver

Convolutional codes are one of the Forward Error Correction (FEC) codes that are used in every robust digital communication system. Viterbi algorithm is employed in wireless communications to decode the convolutional codes. Such decoders are complex and dissipate large amount of power. Software Defined Radio (SDR) is realized using highly configurable hardware platforms. Field Programmable Gate Array technology (FPGA) is a highly configurable option for implementing many sophisticated signal processing tasks in SDR. In this paper, a generic, configurable and low power Viterbi decoder for

Fibonacci-based hardware post-processing for non-autonomous signum hyperchaotic system

This paper presents a hardware implementation of a robust non-autonomous hyperchaotic-based PRNG driven by a 256-bit LFSR. The original chaotic output is post-processed using a novel technique based on the Fibonacci series, bitwise XOR, rotation, and feedback. The proposed post-processing technique preserves the throughput of the system and enhances the randomness in the output which is verified by successfully passing all NIST SP. 800-22 tests. The system is realized on a Xilinx Virtex 4 FPGA achieving throughput up to 13.165 Gbits/s for 16-bit bus-width surpassing previously reported CB

Pagination

- Previous page ‹‹

- Page 52

- Next page ››