Breadcrumb

A Grunwald–Letnikov based Manta ray foraging optimizer for global optimization and image segmentation

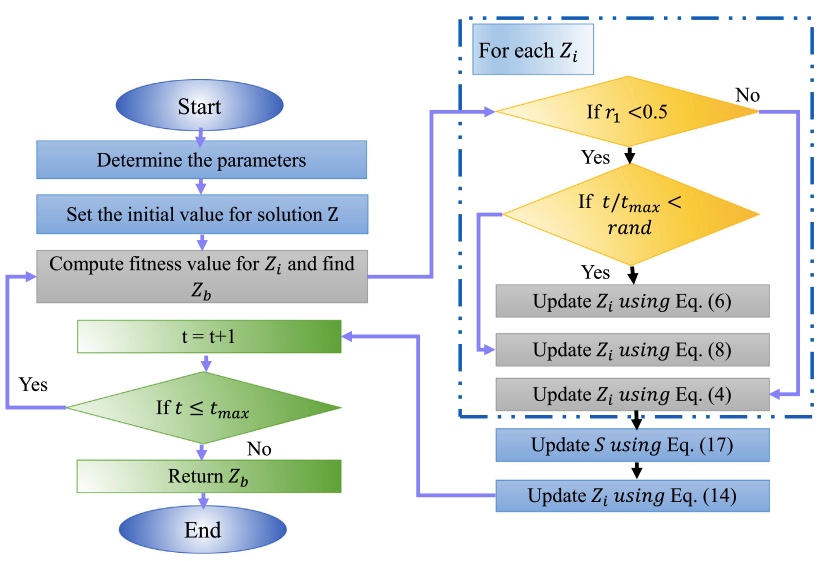

This paper presents a modified version of Manta ray foraging optimizer (MRFO) algorithm to deal with global optimization and multilevel image segmentation problems. MRFO is a meta-heuristic technique that simulates the behaviors of manta rays to find the food. MRFO established its ability to find a suitable solution for a variant of optimization problems. However, by analyzing its behaviors during the optimization process, it is observed that its exploitation ability is less than exploration ability, which makes MRFO more sensitive to attractive to a local point. Therefore, we enhanced MRFO by

Control design approaches for parallel robot manipulators: A review

In this article, different control design approaches for parallel robot manipulators are presented with two distinguished classes of control strategies in the literature. These are the model-free control and the dynamic control strategy, which is mainly a model-based scheme, and is mostly the alternative when the control requirements are more stringent. The authors strongly believe that this paper will be helpful for researchers and engineers in the field of robotic systems. Copyright 2017 Inderscience Enterprises Ltd.

Comparative study of fractional filters for Alzheimer disease detection on MRI images

This paper presents a comparative study of four fractional order filters used for edge detection. The noise performance of these filters is analyzed upon the addition of random Gaussian noise, as well as the addition of salt and pepper noise. The peak signal to noise ratio (PSNR) of the detected images is numerically compared. The mean square error (MSE) of the detected images as well as the execution time are also adopted as evaluation methods for comparison. The visual comparison of the filters capability in medical image edge detection is presented, that can help in the diagnosis of

Advance Interconnect Circuit Modeling Design Using Fractional-Order Elements

Nowadays, the interconnect circuits' conduct plays a crucial role in determining the performance of the CMOS systems, especially those related to nano-scale technology. Modeling the effect of such an influential component has been widely studied from many perspectives. In this article, we propose a new general formula for RLC interconnect circuit model in CMOS technology using the fractional-order elements approach. The study is based on approximating an infinite transfer function of the CMOS circuit with a noninteger distributed RLC load to a finite number of poles. It is accurate due to the

FPGA implementation of a reconfigurable Viterbi decoder for WiMAX receiver

Field Programmable Gate Array technology (FPGA) is a highly configurable option for implementing many sophisticated signal processing tasks in Software Defined Radios (SDRs). Those types of radios are realized using highly configurable hardware platforms. Convolutional codes are used in every robust digital communication system and Viterbi algorithm is employed in wireless communications to decode the convolutional codes. Such decoders are complex and dissipate large amount of power. In this paper, a low power-reconfigurable Viterbi decoder for WiMAX receiver is described using a VHDL code for

FPGA implementation of a configurable viterbi decoder for software radio receiver

Convolutional codes are one of the Forward Error Correction (FEC) codes that are used in every robust digital communication system. Viterbi algorithm is employed in wireless communications to decode the convolutional codes. Such decoders are complex and dissipate large amount of power. Software Defined Radio (SDR) is realized using highly configurable hardware platforms. Field Programmable Gate Array technology (FPGA) is a highly configurable option for implementing many sophisticated signal processing tasks in SDR. In this paper, a generic, configurable and low power Viterbi decoder for

Fibonacci-based hardware post-processing for non-autonomous signum hyperchaotic system

This paper presents a hardware implementation of a robust non-autonomous hyperchaotic-based PRNG driven by a 256-bit LFSR. The original chaotic output is post-processed using a novel technique based on the Fibonacci series, bitwise XOR, rotation, and feedback. The proposed post-processing technique preserves the throughput of the system and enhances the randomness in the output which is verified by successfully passing all NIST SP. 800-22 tests. The system is realized on a Xilinx Virtex 4 FPGA achieving throughput up to 13.165 Gbits/s for 16-bit bus-width surpassing previously reported CB

Cad tool for two-digit ternary functions design

Ternary number, which attracts the research attention for its high capacity, has emerged in many applications, recently. Unlike binary numbers, two bit ternary number involves 93 = 729 different functions while two bit binary number involves only 42 = 16 different possible functions. In this paper, a novel automatic software description two bits ternary functions design tool is presented. Different examples are provided and synthesized to ternary logic circuits. Finally, the presented logic circuits are verified by SPICE simulation using carbon nano-Tube (CNTFET) transistors. © 2019 IEEE.

Controllable OTA Slew-rate for CMOS Image Sensor

In this work, a proposed circuit is implemented using tsmc 0.18um technology of area 16642 um2 with supply voltage equals 5V. A proposed implementation of a controllable Operational Transconductance Amplifier (OTA) slew rate for CMOS image sensor (CIS) is proposed. The slew rate is controlled by switching between various bias circuits for the OTA. The biasing circuit controls the value of OTA biased current, which allows controlling the amplifier's characteristics. As the flicker noise in the main contributor in reducing the quality of image sensors performance. The proposed circuit allows

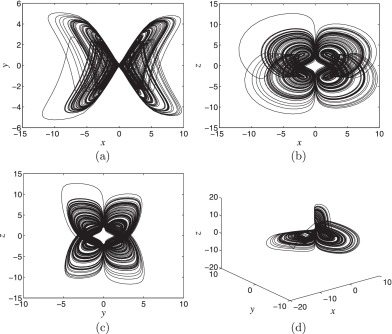

Four-wing attractors in a novel chaotic system with hyperbolic sine nonlinearity

Chaotic systems generating multi-wing attractors have received considerable attention in the literature. In this work, we propose a novel three-dimensional chaotic system with hyperbolic sine nonlinearity. It is worth noting that the system is elegant and includes only one parameter. Despite its simple structure, the new system displays double-wing and four-wing chaotic attractors. By studying dynamics of the system, coexistence of limit cycles or chaotic attractors is discovered. The capable of the synchronization of new chaotic system is verified by using an adaptive control. Furthermore, an

Pagination

- Previous page ‹‹

- Page 12

- Next page ››