Breadcrumb

A collection of interdisciplinary applications of fractional-order circuits

An attractive feature of fractional calculus is its application in various interdisciplinary fields, extending from biomedical and biological notions to mechanical properties. For their description, fractional-order models have outperformed the corresponding integer-order models, resulting in a more realistic behavior, due to the additional degrees of freedom offered and the long-term memory effect that reflects the fractional order. These improved features are processed by appropriate circuit implementations, derived through several approximation methods, whose primary objective is to provide

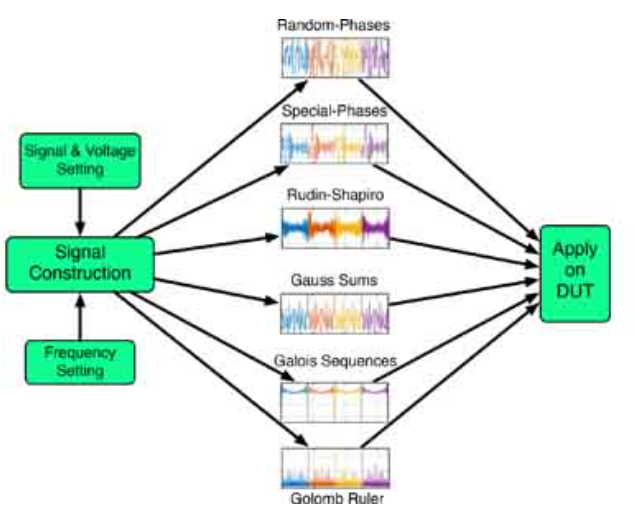

Wide Bandwidth Signals for Joint Time-Frequency Characterization of Nonlinear and Time-Varying Circuits

In this work, we generate and use a total of six different wideband signals for joint time-frequency characterization of nonlinear time-invariant [N-shaped differential resistor (NDR)] and linear time-varying (thermistor) circuits. A data acquisition board is used for applying the signals in the form of a voltage excitation and reading the induced current. The input signals have flat power spectra, thus avoiding the need for iterative calibration loops required to obtain signals with low crest factor. Such iterative loops are unavoidable when using random, pseudorandom, or chaotic signals all

MOS realizations of fractional-order elements

The exploitation of fractional calculus in engineering applications requires the utilization of fractional-order elements. As there is no immediate access to such type of elements, emulators that proportionally imitate their behavior are developed. The realization of emulators of fractional-order elements is based on the approximation of their impedance function. Subsequently, an advantageous option for the circuit implementation of the obtained, approximated impedance function is MOS transistor-based configurations, as they provide a dynamic system with electronically adjustable parameters

Reduce Computing Complexity of Deep Neural Networks Through Weight Scaling

Large deep neural network (DNN) models are computation and memory intensive, which limits their deployment especially on edge devices. Therefore, pruning, quantization, data sparsity and data reuse have been applied to DNNs to reduce memory and computation complexity at the expense of some accuracy loss. The reduction in the bit-precision results in loss of information, and the aggressive bit-width reduction could result in noticeable accuracy loss. This paper introduces Scaling-Weight-based Convolution (SWC) technique to reduce the DNN model size and the complexity and number of arithmetic

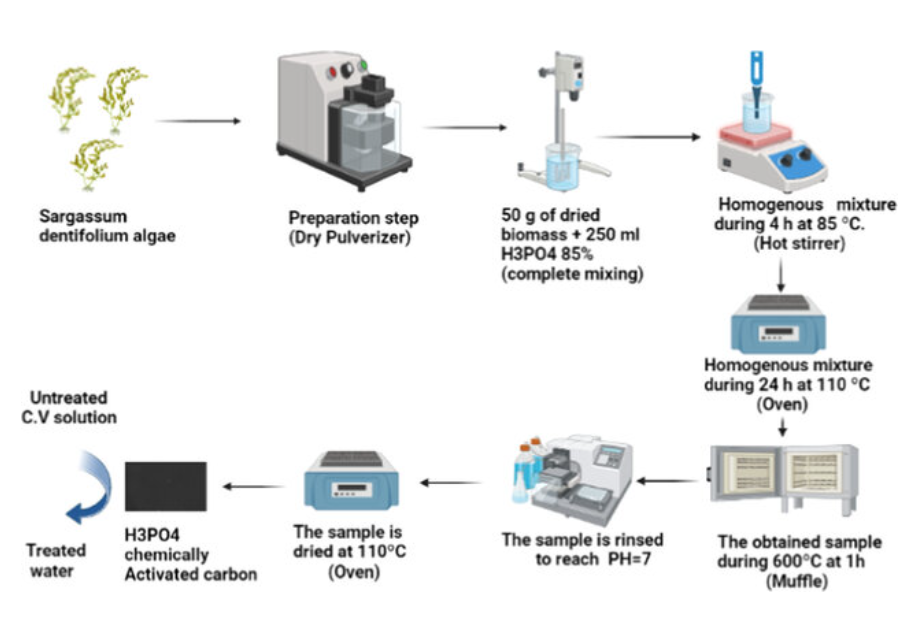

Crystal violet removal using algae-based activated carbon and its composites with bimetallic Fe0-Cu

The textile industry is considered a source of pollution because of the discharge of dye wastewater. The dye wastewater effluent has a significant impact on the aquatic environment. According to the World Bank, textile dyeing, and treatment contribute 17 to 20% of the pollution of water. This paper aims to prepare the bimetallic nano zero-valent iron-copper (Fe0-Cu), algae-activated carbon, and their composites (AC-Fe0-Cu), which are employed as adsorbents. In this paper, Synthetic adsorbents are prepared and examined for the adsorption and removal of soluble cationic crystal violet (CV) dye

Approximation and realization of power-law all-pass filters

Non-integer power-law all-pass transfer functions, are approximated by suitable integer-order transfer functions in this work. The derivation of the integer-order transfer functions is based on the analytic expansion of the (non-integer) power-law transfer functions through the utilization of the binomial theorem. The offered benefit is the derivation of stable integer-order transfer functions. This study is supported by experimental results, obtained using a Field Programmable Analog Array device, after the employment of curve fitting based approximation techniques. © 2022 Elsevier GmbH

Implementation and Experimental Verification of Resistorless Fractional-Order Basic Filters

Novel structures of fractional-order differentiation and integration stages are presented in this work, where passive resistors are not required for their implementation. This has been achieved by considering the inherent resistive behavior of fractional-order capacitors. The implementation of the presented stages is performed using a current feedback operational amplifier as active element and fractional-order capacitors based on multi-walled carbon nano-tubes. Basic filter and controller stages are realized using the introduced fundamental blocks, and their behavior is evaluated through

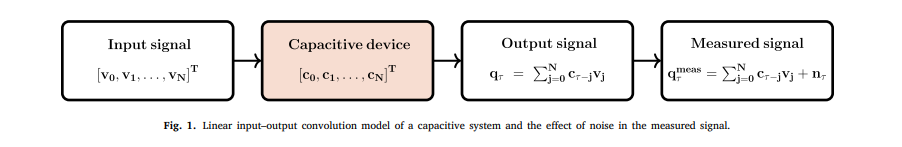

Tikhonov regularization for the deconvolution of capacitance from the voltage–charge response of electrochemical capacitors

The capacitance of capacitive energy storage devices cannot be directly measured, but can be estimated from the applied input and measured output signals expressed in the time or frequency domains. Here the time-domain voltage–charge relationship of non-ideal electrochemical capacitors is treated as an ill-conditioned convolution integral equation where the unknown capacitance kernel function is to be found. This comes from assuming a priori that in the frequency domain the charge is equal to the product of capacitance by voltage, which is in line with the definition of electrical impedance

Synthesis of resonance-based common-gate fully differential band-pass filters

We propose a class of fully differential filters based on a common-gate differential amplifier cell in three different topologies. Our focus is on the synthesis of second-order band-pass filters and we found 53 possible circuits. All filters are resonance-based and have electronically tunable gain. Post layout simulations in 65-nm CMOS technology are provided to validate the proper function of these filters. © 2022 Elsevier B.V.

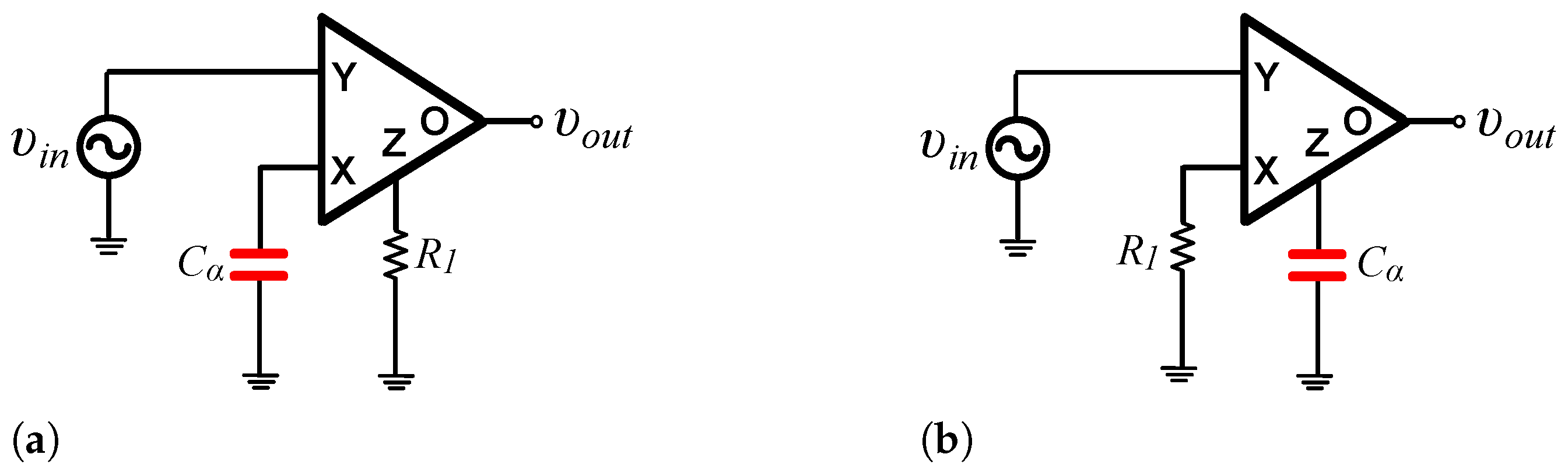

Fractional-order inverse filters revisited: Equivalence with fractional-order controllers

The equivalence of fractional-order inverse filters with fractional-order controllers is demonstrated in this work. This is achieved by appropriately rewriting the filters transfer functions in order to clarify the correspondence between the gain and time-constant of the filters and the scaling factor and differentiation/integration constant of the controllers. Possible implementations of fractional-order inverse filters using second generation voltage conveyors are presented and an application example, related to the control of a motion system, is demonstrated for evaluating the behavior of

Pagination

- Previous page ‹‹

- Page 18

- Next page ››