Breadcrumb

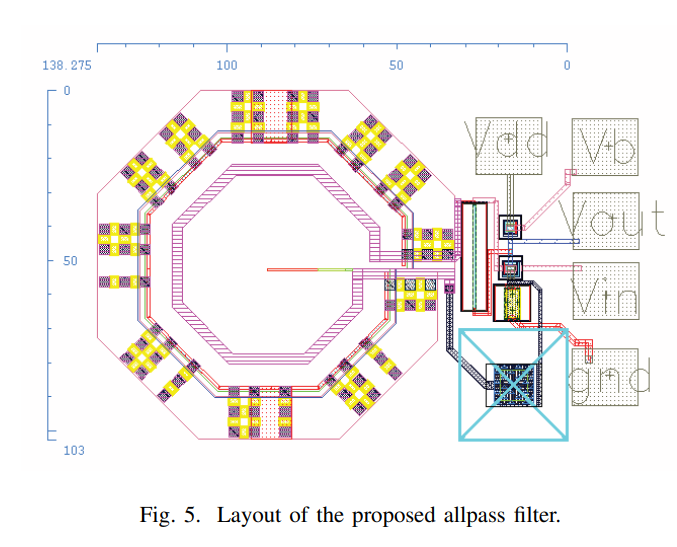

An Ultra-Low Power Wide-Band Single-Transistor Second-Order Allpass Filter in 65nm CMOS

In this paper, we propose a MOS design of a second-order voltage-mode allpass filter to be used as a time delay cell. The proposed filter is based on a single transistor, three resistors and two energy storage elements and was designed in a 65nm CMOS technology. Post-layout simulations demonstrate a group delay of approximately 13ps across a 30GHz bandwidth, while only consuming 809.7μW from a 1-V supply. As a proof of concept, the proposed filter was constructed and verified experimentally using discrete MOS transistors. The experimental results show a group delay of approximately 370ns

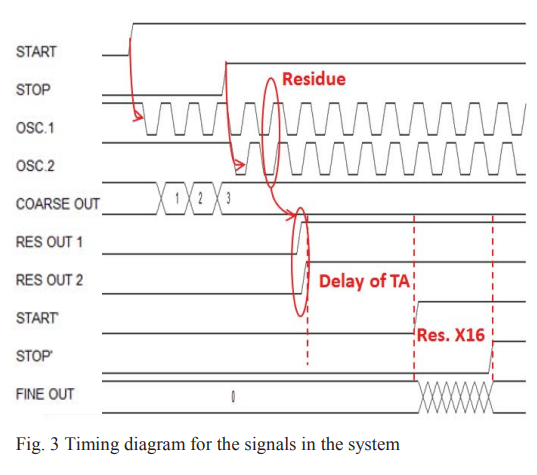

A novel high throughput high resolution two-stage oscillator-based TDC

This paper presents a new technique to reduce the conversion time, hence improve the throughput, of the two-stage Time to Digital Converter (TDC) architecture. An oscillator based TDC is used in the first and second stages. The time residue from the first stage is generated directly after the stop signal is asserted and saved in the form of phase-shift between two oscillating signals. A throughput of 400 MS/s, a DNL of 0.38, and an INL of 0.36 are achieved. © 2013 IEEE.

Low power clock generator using charge recycling

A major portion of the power consumed in today's systems is due to the clock distribution network. Solutions attempted to reduce clocking power result in low efficiency systems or systems with high complexity control schemes. In this work, a low power clock generator is introduced that can reduce switching power of the clock by almost 75%. This circuit uses the charge recycling concept to achieve such power reduction while utilizing a simple control technique. ©2010 IEEE.

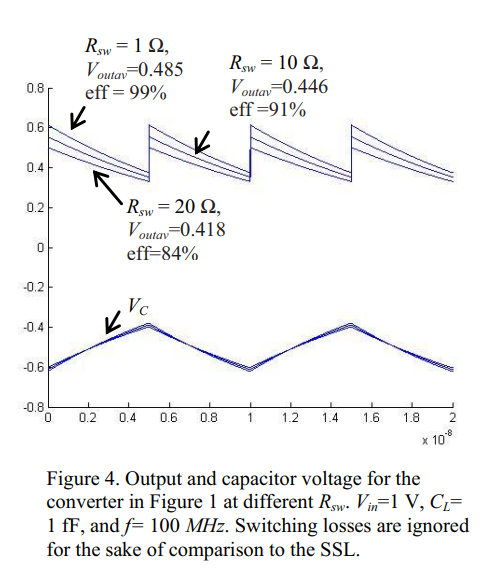

On the accuracy of commonly used loss models in SCVRs

[No abstract available]

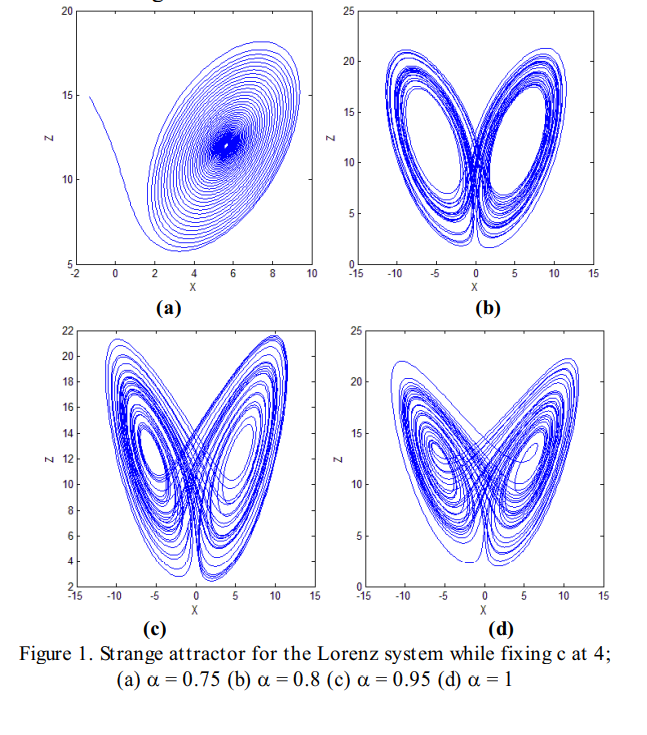

Image encryption in the fractional-order domain

This paper presents a new image encryption scheme based on the fractional-order Lorenz system which gives more degrees of freedom in key generation. In the modified fractional-order system, the key length is doubled using the three fractional-orde r parameters beside the three initial conditions, which makes it invulnerable to brute-force attacks. In addition, using a very simple algorithm, based on pixel confusion only, strongly encrypted images are produced. Such an algorithm can be used in real time applications. To evaluate the algorithm and analyze the encryption results, a standard image

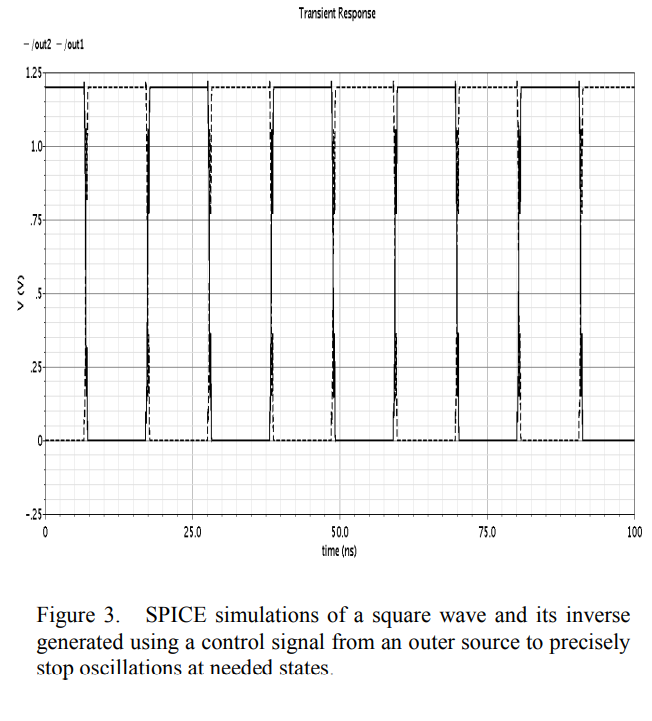

Design methodology for square wave resonant clock generators

Resonant clocking is a promising low power alternative for conventional clocking method. In this work, a design methodology is presented for square wave resonant clocking technique to assure minimum power consumption. These equations were verified by designing a differential clock generator which showed 55% power savings compared to conventional clocking. © 2012 IEEE.

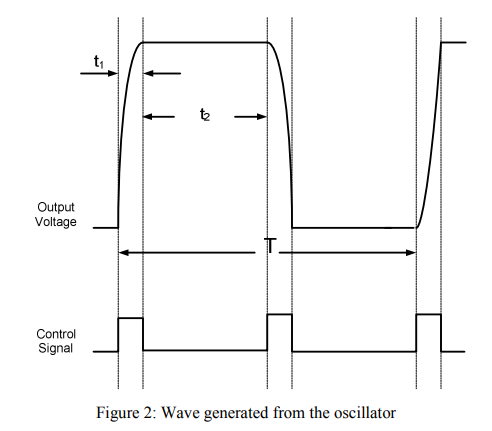

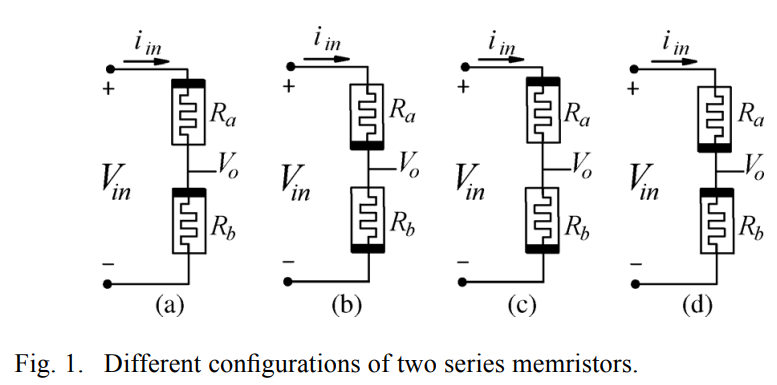

Generalized analysis of symmetric and asymmetric memristive two-gate relaxation oscillators

Memristive oscillators are a novel topic in nonlinear circuit theory, where the behavior of the reactive elements is emulated by the memristor. This paper presents symmetric and asymmetric memristive two-gate relaxation oscillators. First, the analysis of the two series memristors is introduced to study the effect of changing their polarities, as well as the mobility factor to be used in the two-gate relaxation oscillator instead of the RC circuit. The generalized analysis for the proposed memristive two-gate oscillator is introduced, where the generalized expressions for the oscillation

Current source based standard-cell model for accurate timing analysis of combinational logic cells

Timing verification is an essential process in nanometer design. Therefore, static timing analysis (STA) is currently the main aspect of performance verification. Traditional STA is based on lookup tables with input slew and output load capacitance. It is becoming insufficient to accurately characterize many significant aspects of the conventional cell delays models, such as: the process variations, nonlinear waveforms, nonlinear loads, and multiple inputs switching (MIS). Therefore, the current trend in modern designs is to use current source based models (CSM), which model MOSFETs as a

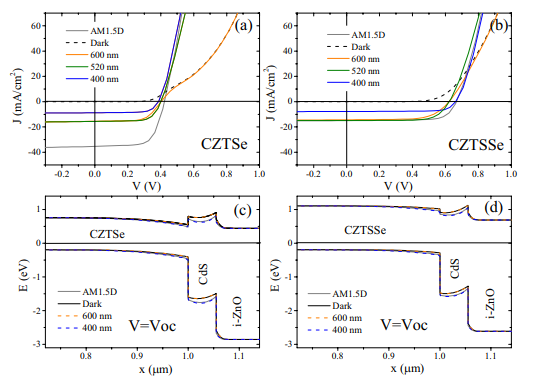

Spectral current-voltage analysis of kesterite solar cells

Current-voltage analysis using different optical band pass filters has been performed on Cu2ZnSnSe4 and Cu2ZnSn(S,Se) 4 thin-film solar cells. When using red or orange light (i.e. wavelengths above 600 nm), a distortion appears in the I-V curve of the Cu 2ZnSnSe4 solar cell, indicating an additional potential barrier to the current flow in the device for these conditions of illumination. This barrier is reduced when using a Cu2ZnSn(S,Se)4 absorber. Numerical simulations demonstrate that the barrier visible under red light could be explained by a positive conduction band offset at the front

On the mathematical modeling of memcapacitor bridge synapses

Mem-element based synaptic bridge is very promising topic due to its learning capability where the synaptic bridge can be build using either memristors or memcapacitors. In this paper, the detailed mathematical analysis of memcapacitor bridge circuit is introduced. This mathematical analysis is build when a current input signal is applied to excite the bridge. Closed form expressions for the required pulse width; synaptic weight; and conditions for positive, negative and zero synaptic weight are derived. The obtained expressions are verified using SPICE simulations showing very good matching.

Pagination

- Previous page ‹‹

- Page 25

- Next page ››